# PIO-48.PC104

User Manual | 3701

## **Contents**

| CONTENTS                            | 2  |

|-------------------------------------|----|

| INTRODUCTION                        | 3  |

| BEFORE YOU GET STARTED              | 4  |

| CARD SETUP                          | 7  |

| SOFTWARE INSTALLATION               | 9  |

| PHYSICAL INSTALLATION               | 11 |

| DIGITAL I/O INTERFACE               | 12 |

| PROGRAMMING THE PIO-48.PC104        | 15 |

| ELECTRICAL CHARACTERISTICS          | 19 |

| SPECIFICATIONS                      | 20 |

| EXAMPLE CIRCUITS                    | 21 |

| APPENDIX A - TROUBLESHOOTING        | 22 |

| APPENDIX B - HOW TO GET ASSISTANCE  | 23 |

| APPENDIX C - SILK SCREEN - 3701 PCB | 24 |

| APPENDIX D - COMPLIANCE NOTICES     | 25 |

| WARRANTY                            | 26 |

## Introduction

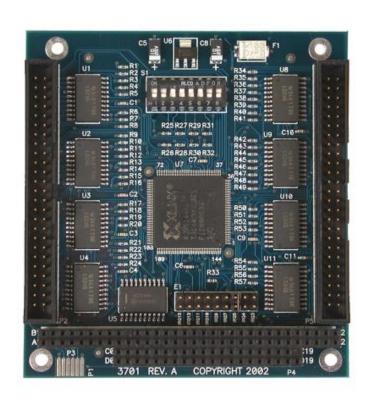

The PIO-48.PC104 part number 3701 digital I/O interface provides 48 channels of buffered drive digital I/O emulating 8255 mode zero. The PIO-48.PC104 can be utilized for a variety of control and automation applications including control and monitoring of TTL devices (e.g., LEDs, small solenoids, small relays) and interfacing to solid-state relay racks (SSRs) for high-power AC or DC loads.

The PIO-48.PC104's 48 digital I/O channels are accessed via two 50-pin header connectors with industry-standard pin out. Each header provides 24 bits of digital I/O divided into two eight-bit ports and two four bit ports for upper and lower nibble. Each port may be individually configured via software command as input or output to best match your particular application requirements.

The PIO-48.PC104 is designed to be used with a variety of Operating Systems including Windows 98/NT/ME/2000/XP and DOS. The Seal/O API (Application Programmer Interface) is available upon request and provides a variety of useful high-level function calls implemented as a Windows dynamic link library (DLL). In addition to the API, Seal/O includes sample code and utilities to simplify software development.

### Other Sealevel PC104 Digital I/O Products

| Model        | Part No.   | Description                                   |

|--------------|------------|-----------------------------------------------|

| DIO-104.REL  | (P/N 3710) | - 16 Reed Relays                              |

| DIO-104.0PTO | (P/N 3720) | - 16 Optically Isolated Inputs                |

| DIO-32.104   | (P/N 3730) | - 16 Optically Isolated Inputs/16 Reed Relays |

## **Before You Get Started**

### What's Included

The PIO-48.PC104 is shipped with the following items. If any of these items are missing or damaged, please contact Sealevel for replacement.

Item# 3701 - PIO-48.PC104 Adapter

### **Advisory Conventions**

#### Warning

The highest level of importance used to stress a condition where damage could result to the product, or the user could suffer serious injury.

#### **Important**

The middle level of importance used to highlight information that might not seem obvious or a situation that could cause the product to fail.

#### Note

The lowest level of importance used to provide background information, additional tips, or other non-critical facts that will not affect the use of the product.

### **Optional Items**

Depending upon your application, you are likely to find one or more of the following items useful for interfacing the PIO-48.PC104 to real-world signals. All items can be purchased from our website (<a href="https://www.sealevel.com">www.sealevel.com</a>) or by calling 864-843-4343.

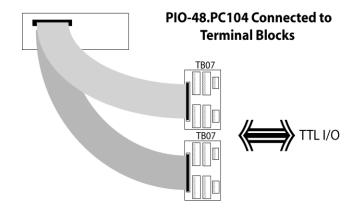

#### For TTL applications:

#### Terminal Block Kit - (Part Number KT107)

Kit includes the TB07 screw terminal block and CA167 ribbon cable for connecting one of the PIO-48.PC104's 50-pin header connectors to your I/O. 6" Snap track and DIN rail clips are included for DIN rail mounting.

#### • IDC 50 to IDC 50 Pin 40" Ribbon Cable (Part Number CA167)

Interfaces each of the PIO-48.PC104's 50-pin header connectors.

#### Simulation/debug module (Part Number TA01)

Module allows monitoring status of output pins and controlling state of input pins. An LED corresponding to each port bit illuminates to indicate state. Eight position DIP-switches are used to generate input status changes.

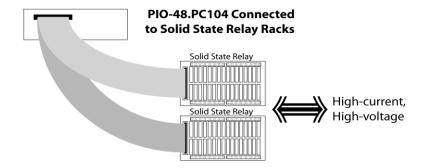

#### For high-current, high-voltage applications:

#### IDC 50 to IDC 50 Pin Ribbon Cable (Part Number CA167)

40" cable connects the PIO-96.PCI to solid-state relay racks equipped with 50-pin header interface.

#### • IDC 50 to IDC 50 Pin Ribbon Cable (Part Number CA135)

40" cable connects the PIO-96.PCI to solid-state relay racks equipped with 50-pin edge connector.

#### • Solid-State Relay Racks:

#### **Quad six position relay rack (Part Number PB24HQ)**

Relay rack can accept up to six QSSRs for a total of 24 channels. Features a 50-pin header connector for easy interface via 50-conductor ribbon cables.

#### Quad four position relay rack (Part Number PB16HQ)

Relay rack can accept up to four QSSRs for a total of 16 channels. Features a 50-pin header connector for easy interface via 50-conductor ribbon cables.

#### • Quad Solid-State Relay Modules:

#### AC Input (Part Number IA5Q)

Provides 4 channels of discrete I/O interface to monitor AC inputs up to 140V @ 10mA.

#### DC Input (Part Number IB5Q)

Provides 4 channels of discrete I/O interface to monitor DC inputs from 3.3V to 32V.

#### AC Output (Part Number OA5Q)

Provides 4 channels of discrete I/O interface to control AC outputs up to 140V @ 3A.

#### DC Output (Part Number OB5Q)

Provides 4 channels of discrete I/O interface to control DC outputs up to 60V @ 3A.

#### Simulation/debug module (Part Number TA01)

Module simulates the operation and load characteristics of a standard 24-channel relay rack. An LED corresponding to each port bit illuminates to indicate state. Eight position DIP-switches are used to generate input status changes.

## **Card Setup**

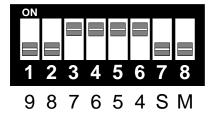

### **Address Selection**

The PIO-48.PC104 occupies 8 consecutive I/O locations. The DIP-switch (S1) is used to set the base address for these locations and the IRQ mode options. Be careful when selecting the base address as some selections conflict with existing PC ports. The following table shows several examples that usually do not cause a conflict.

|             |              | Α9  | A8  | A7  | A6 | A5  | A4 |

|-------------|--------------|-----|-----|-----|----|-----|----|

| Hex Address | Binary       | 1   | 2   | 3   | 4  | 5   | 6  |

| 100-107     | 01 0000 xxxx | On  | Off | On  | On | On  | On |

| 180-187     | 01 1000 xxxx | On  | Off | Off | On | On  | On |

| 200-207     | 10 0000 xxxx | Off | On  | On  | On | On  | On |

| 280-287     | 10 1000 xxxx | Off | On  | Off | On | On  | On |

| 300-307     | 11 0000 xxxx | Off | Off | On  | On | On  | On |

| 380-387     | 11 1000 xxxx | Off | Off | Off | On | On  | On |

| 3A0-3A7     | 11 1010 xxxx | Off | Off | Off | On | Off | On |

#### **Interface Selection**

DIP-Switch positions 'S' and 'M' on switch S1 selects the interrupt mode for each adapter.

With the 'S' selected, the adapter is in a (S)hared interrupt mode, which allows more than one adapter to access a single IRQ.

'M' indicates the inclusion of a 1K-ohm pull-down resistor required on one adapter when sharing interrupts.

Set the switch to 'S' for shared interrupt mode on all adapters sharing an IRQ. On one of the adapters sharing an interrupt set the switches for both 'S' and for 'M'. This provides the pull-down resistor circuit that makes sharing IRQs possible. If you are using more than one compatible adapter in a bus you should only have one adapter set to 'M'.

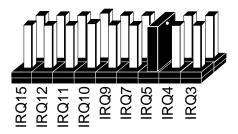

### **IRQ Selection**

The PIO-48.PC104 has an interrupt selection jumper, which should be set prior to use, if an interrupt is required by your application software. Consult the user manual for the application software being used to determine the proper setting.

The supplied driver for Windows and does not require, nor does it support interrupts. It is recommended that this jumper be removed to prevent any resource conflicts.

## **Software Installation**

#### Windows 98/ME/2000/XP Installation

- Begin by locating, selecting, and installing the correct software from the <u>Sealevel software driver</u> database.

- 2. Select the Part Number (3701) for your adapter from the listing.

- 3. Select 'Download Now" for the SealO Classic for Windows. The setup file will automatically detect the operating environment and install the proper components. Next (depending on your browser) select the 'Run this program from its current location' or 'Open' option. Follow the information presented on the screens that follow. During setup the user may specify installation directories and other preferred configurations. This program also adds entries to the system registry that are necessary for specifying the operating parameters for each driver. An uninstall option is also available to remove SealO files and registry/INI file entries from the system.

- 4. A screen may appear with the declaration: "The publisher cannot be determined due to the problems below: Authenticode signature not found." Please select the 'Yes' button and proceed with the installation. This declaration simply means that the Operating System is not aware of the driver being loaded. It will not cause any harm to your system.

- 5. During setup, the user may specify installation directories and other preferred configurations. This program also adds entries to the system registry that are necessary for specifying the operating parameters for each driver. An uninstall option is also included to remove all registry/INI file entries from the system.

- 6. If installing in NT, skip to 'Windows NT Card Installation' step 13.

- 7. Go to the "Add New Hardware Wizard" in the Control Panel.

- 8. When the Wizard asks if you want Windows to search for the new hardware, choose "No, I want to select the hardware from a list."

- Scroll through the list of categorized hardware and select 'SealO Devices'. If this is the first SealO

device you may need to select 'Other Devices' and 'Sealevel Systems, Inc.' instead of 'SealO

Devices'.

- 10. Click "Next".

- 11. Select the card model and press "Next".

- 12. The Wizard will guide you through a few more informational prompts; continue to click "Next" until it is completed.

- 13. Your card's resource assignments may be adjusted through the Device Manager (if, for instance, you need to change the I/O port address Windows assigned when you installed the card).

- 14. Windows software installation is complete

- 15. Windows NT Card Installation: After accomplishing steps 1 3, bring up the Control Panel and double-click on the SealO Devices icon. To install a new card, click "Add Port". Repeat this procedure for as many SealO cards as you wish to install.

## **Physical Installation**

Extreme care should be taken when installing the PIO-48.PC104 to avoid causing damage to the connectors. After the adapter is installed, connect your I/O cables to P2 and P5. Please note these headers are keyed so that pin 1 of the cable matches pin 1 of the connector. Refer to <u>Card Setup</u> for information on setting the address and jumper options before inserting the PIO-48.PC104 onto the stack.

Do not install the Adapter in the machine until the software has been fully installed.

- 1. Turn off power. Disconnect the power cord.

- Gently insert the PIO-48.PC104 connector noting proper key orientation of the expansion connector on a PC/104 compatible card. The PIO-48.PC104 adapter is keyed per the current PC/104 Specification. This will aid in preventing the adapter from being inserted incorrectly.

- 3. Mounting hardware (nylon stand-offs and screws) is provided to ensure a good mechanical connection. Retain any mounting hardware not used to allow for future expansion.

- 4. The cables provided are keyed and can be installed before or after the adapter is inserted in the stack.

- 5. Connect the power cord and power up the machine.

The PIO-48.PC104 is now ready for use.

### 3<sup>rd</sup> Party Software

For the most up to date information on third party software support, please visit:

https://www.sealevel.com/support/3rd-party-software-support/.

## Digital I/O Interface

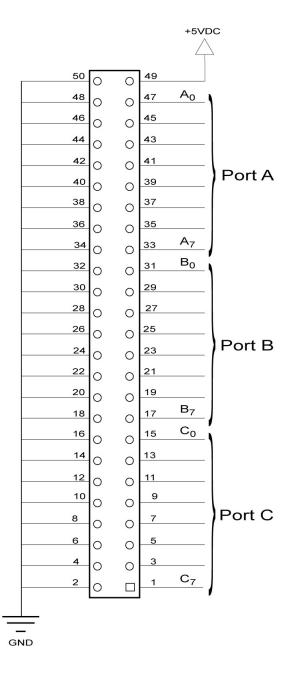

The PIO-48.PC104's 48 digital I/O channels are accessed via two industry-standard 50-pin header connectors. Each header provides 24 bits of digital I/O divided into two eight-bit ports and two four bit ports for upper and lower nibble. Each port may be individually configured via software command as input or output.

### **50-pin Header Connectors**

Each of the 50-pin connectors has the following pin out which is compatible with a wide variety of solid state relay racks:

## **Pull Ups**

Eight resistors are installed to provide pull-ups to the input ports. These are installed on all ports. The pull-up resistors are rated at 10K ohms. Figure 4 below provides the resistors and corresponding port. The resistors ensure that no line is floating which is not connected. This provides consistent biasing on all unterminated lines.

| Corresponding Port |

|--------------------|

| Port A1            |

| Port B1            |

| Port C1L           |

| Port C1U           |

| Port A2            |

| Port B2            |

| Port C2L           |

| Port C2U           |

|                    |

### **Physical Connection**

The port signals for the PIO-48.PC104 are physically connected via two 50-pin box headers. P5 provides the connections for ports A1-C1 and P2 provide the connections for A2-C2. These headers are compatible with the industry standard 50-pin ribbon/IDC type cabling. This allows for a direct cabling connection between the PIO-48.PC104 and a Solid State Relay Rack (i.e., PB-8. PB-16, PB-24 etc.)

The following table shows the correlation between the port addresses and the 50-pin connections.

| Port A   A0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Description | Pin #         |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------|--|--|--|

| A1       45         A2       43         A3       41         A4       39         A5       37         A6       35         A7       33         Port B         B0       31         B1       29         B2       27         B3       25         B4       23         B5       21         B6       19         B7       17         Port C         C0L       15         C1L       13         C2L       11         C3L       9         C4U       7         C5U       5         C6U       3         C7U       1             | Po          | ort A         |  |  |  |

| A2       43         A3       41         A4       39         A5       37         A6       35         A7       33         Port B         B0       31         B1       29         B2       27         B3       25         B4       23         B5       21         B6       19         B7       17         Port C         C0L       15         C1L       13         C2L       11         C3L       9         C4U       7         C5U       5         C6U       3         C7U       1         GND       All Even pins | A0          | 47            |  |  |  |

| A3       41         A4       39         A5       37         A6       35         A7       33         Port B         B0       31         B1       29         B2       27         B3       25         B4       23         B5       21         B6       19         B7       17         Port C         C0L       15         C1L       13         C2L       11         C3L       9         C4U       7         C5U       5         C6U       3         C7U       1         GND       All Even pins                     | A1          | 45            |  |  |  |

| A4       39         A5       37         A6       35         A7       33         Port B         B0       31         B1       29         B2       27         B3       25         B4       23         B5       21         B6       19         B7       17         Port C         C0L       15         C1L       13         C2L       11         C3L       9         C4U       7         C5U       5         C6U       3         C7U       1         GND       All Even pins                                         | A2          | 43            |  |  |  |

| A5       37         A6       35         A7       33         Port B         B0       31         B1       29         B2       27         B3       25         B4       23         B5       21         B6       19         B7       17         Port C         C0L       15         C1L       13         C2L       11         C3L       9         C4U       7         C5U       5         C6U       3         C7U       1         GND       All Even pins                                                             | A3          | 41            |  |  |  |

| A6       35         A7       33         Port B         B0       31         B1       29         B2       27         B3       25         B4       23         B5       21         B6       19         B7       17         Port C         C0L       15         C1L       13         C2L       11         C3L       9         C4U       7         C5U       5         C6U       3         C7U       1         GND       All Even pins                                                                                 | A4          | 39            |  |  |  |

| A7     33       Port B       B0     31       B1     29       B2     27       B3     25       B4     23       B5     21       B6     19       B7     17       Port C       C0L     15       C1L     13       C2L     11       C3L     9       C4U     7       C5U     5       C6U     3       C7U     1       GND     All Even pins                                                                                                                                                                               | A5          | 37            |  |  |  |

| Port B     B0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | A6          | 35            |  |  |  |

| B0     31       B1     29       B2     27       B3     25       B4     23       B5     21       B6     19       B7     17       Port C       C0L     15       C1L     13       C2L     11       C3L     9       C4U     7       C5U     5       C6U     3       C7U     1       GND     All Even pins                                                                                                                                                                                                            | A7          | 33            |  |  |  |

| B1     29       B2     27       B3     25       B4     23       B5     21       B6     19       B7     17       Port C       C0L     15       C1L     13       C2L     11       C3L     9       C4U     7       C5U     5       C6U     3       C7U     1       GND     All Even pins                                                                                                                                                                                                                            | Po          | ort B         |  |  |  |

| B2     27       B3     25       B4     23       B5     21       B6     19       B7     17       Port C       C0L     15       C1L     13       C2L     11       C3L     9       C4U     7       C5U     5       C6U     3       C7U     1       GND     All Even pins                                                                                                                                                                                                                                            | B0          | 31            |  |  |  |

| B3     25       B4     23       B5     21       B6     19       B7     17       Port C       C0L     15       C1L     13       C2L     11       C3L     9       C4U     7       C5U     5       C6U     3       C7U     1       GND     All Even pins                                                                                                                                                                                                                                                            | B1          | 29            |  |  |  |

| B4     23       B5     21       B6     19       B7     17       Port C       C0L     15       C1L     13       C2L     11       C3L     9       C4U     7       C5U     5       C6U     3       C7U     1       GND     All Even pins                                                                                                                                                                                                                                                                            | B2          | 27            |  |  |  |

| B5     21       B6     19       B7     17       Port C       C0L     15       C1L     13       C2L     11       C3L     9       C4U     7       C5U     5       C6U     3       C7U     1       GND     All Even pins                                                                                                                                                                                                                                                                                            | B3          | 25            |  |  |  |

| B6     19       B7     17       Port C       C0L     15       C1L     13       C2L     11       C3L     9       C4U     7       C5U     5       C6U     3       C7U     1       GND     All Even pins                                                                                                                                                                                                                                                                                                            | B4          | 23            |  |  |  |

| B7         17           Port C           C0L         15           C1L         13           C2L         11           C3L         9           C4U         7           C5U         5           C6U         3           C7U         1           GND         All Even pins                                                                                                                                                                                                                                            | B5          | 21            |  |  |  |

| Port C  COL 15  C1L 13  C2L 11  C3L 9  C4U 7  C5U 5  C6U 3  C7U 1  GND All Even pins                                                                                                                                                                                                                                                                                                                                                                                                                             | В6          | 19            |  |  |  |

| COL         15           C1L         13           C2L         11           C3L         9           C4U         7           C5U         5           C6U         3           C7U         1           GND         All Even pins                                                                                                                                                                                                                                                                                     | B7          | 17            |  |  |  |

| C1L         13           C2L         11           C3L         9           C4U         7           C5U         5           C6U         3           C7U         1           GND         All Even pins                                                                                                                                                                                                                                                                                                              | Po          | ort C         |  |  |  |

| C2L         11           C3L         9           C4U         7           C5U         5           C6U         3           C7U         1           GND         All Even pins                                                                                                                                                                                                                                                                                                                                       | C0L         | 15            |  |  |  |

| C3L 9 C4U 7 C5U 5 C6U 3 C7U 1 GND All Even pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | C1L         | 13            |  |  |  |

| C4U         7           C5U         5           C6U         3           C7U         1           GND         All Even pins                                                                                                                                                                                                                                                                                                                                                                                        | C2L         | 11            |  |  |  |

| C5U 5 C6U 3 C7U 1 GND All Even pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | C3L         | 9             |  |  |  |

| C6U         3           C7U         1           GND         All Even pins                                                                                                                                                                                                                                                                                                                                                                                                                                        | C4U         | 7             |  |  |  |

| C7U         1           GND         All Even pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C5U         | 5             |  |  |  |

| GND All Even pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C6U         | 3             |  |  |  |

| <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | C7U         | 1             |  |  |  |

| <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |               |  |  |  |

| +5\/ /0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | GND         | All Even pins |  |  |  |

| 100 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | +5V         | 49            |  |  |  |

## Programming the PIO-48.PC104

Sealevel's <u>Seal/O software</u> is accessible at Sealevel Systems' website and will be able to assist in the development of reliable applications for the Sealevel Systems family of digital I/O adapters. Included in the Seal/O software are driver functions for use in accessing the I/O as well as helpful samples and utilities.

### **Programming for Windows**

The Seal/O API (Application Programmer Interface) provides a variety of useful high-level function calls implemented in a Windows dynamic link library (DLL). The API is defined in the help file (Start/Programs/SealO/SealO Help) under "Application Programmers Interface". This help file also includes detailed information dealing with installation / removal of the software and information about latency, logic states, and device configuration.

For C language programmers we recommend using the API to access the PIO-48.PC104. If you are programming in Visual Basic, using the ActiveX control included with Seal/O is advised.

### Samples and Utilities

A variety of sample programs and utilities (both executable and source code) are available upon request with Seal/O.

#### **Direct Hardware Control**

In systems where the user's program has direct access to the hardware (DOS) the tables that follow give the mapping and functions that the PIO-48.PC104 provides.

### **Reading the Inputs**

The inputs are active high. If an input is driven high (2V to 5.25 V) it will read as a logical one, if driven low (0V to 0.8V) it will read as a logical zero. If an input is not driven it will read as a one due to the 10K ohm pull up resistors on each port.

### Reading the Outputs

The value that is currently being used to drive the outputs will be returned.

### **Presetting an Output Port**

Each port has an output register associated with it. This register may be written and retains its value whether the port is configured as an input or an output. To preset the value of an output port the program should write to the port when it is configured as an input then configure it as an output.

### Writing the Outputs

The outputs are active high. Writing a one (1) corresponds to 5V while writing a zero (0) corresponds to 0V, at the output.

#### Port C

Port C is written and read to as two four-bit ports. If both lower and upper nibbles are configured the same then no special considerations need to be made. But if they are configured differently, one nibble as input, and one as output then the user will have to keep this in mind. When reading, the input will be returned on the corresponding upper or lower nibble while the current outputs will be returned on their corresponding upper or lower nibble. When writing, the corresponding nibble will be written to the output nibble, while the input nibble will have its output register written to. The output register can be written to without affecting the inputs.

### **Register Description**

| Address     |                               | Mode  | D7    | D6    | D5    | D4     | D3    | D2     | D1     | D0     |

|-------------|-------------------------------|-------|-------|-------|-------|--------|-------|--------|--------|--------|

| Base+0      | Port A1                       | RD/WR | PA1D7 | PA1D6 | PA1D5 | PA1D4  | PA1D3 | PA1D2  | PA1D1  | PA1D0  |

| Base+1      | Port B1                       | RD/WR | PB1D7 | PB1D6 | PB1D5 | PB1D4  | PB1D3 | PB1D2  | PB1D1  | PB1D0  |

| Base+2      | Port C1                       | RD/WR | PC1D7 | PC1D6 | PC1D5 | PC1D4  | PC1D3 | PC1D2  | PC1D1  | PC1D0  |

| Base+3      | Control Word Port 1           | WR    | 0     | 0     | 0     | CW1D4  | CW1D3 | 0      | CW1D1  | CW1D0  |

| Base+4      | Interrupt config Port 1       | RD/WR | 0     | 0     | 0     | 0      | 0     | IRQEN1 | IRQC11 | IRQC10 |

| Base+5      | Interrupt status Port 1 and 2 | RD    | 0     | 0     | 0     | IRQST2 | 0     | 0      | 0      | IRQST1 |

| Base+8      | Port A2                       | RD/WR | PA2D7 | PA2D6 | PA2D5 | PA2D4  | PA2D3 | PA2D2  | PA2D1  | PA2D0  |

| Base+9      | Port B2                       | RD/WR | PB2D7 | PB2D6 | PB2D5 | PB2D4  | PB2D3 | PB2D2  | PB2D1  | PB2D0  |

| Base+A (10) | Port C2                       | RD/WR | PC2D7 | PC2D6 | PC2D5 | PC2D4  | PC2D3 | PC2D2  | PC2D1  | PC2D0  |

| Base+B (11) | Control Word Port 2           | WR    | 0     | 0     | 0     | CW2D4  | CW2D3 | 0      | CW2D1  | CW2D0  |

| Base+C (12) | Interrupt config Port 2       | RD/WR | 0     | 0     | 0     | 0      | 0     | IRQEN2 | IRQC21 | IRQC20 |

## **I/O Control Word**

Each port may be configured as either Input or Output. This is accomplished by writing the correct Control Word (CW) to the proper register.

| CWnD0 | Port C1 lower nibble (bits 0-3)            | 1 = input                                                       | 0 = output | 1 on power up |  |  |  |

|-------|--------------------------------------------|-----------------------------------------------------------------|------------|---------------|--|--|--|

| CWnD1 | Port B1                                    | 1 = input                                                       | 0 = output | 1 on power up |  |  |  |

| CWnD2 | C                                          | or 1 (no effect)                                                |            |               |  |  |  |

| CWnD3 | Port C1 upper nibble (bits 4-7)            | Port C1 upper nibble (bits 4-7) 1 = input 0 = output 1 on power |            |               |  |  |  |

| CWnD4 | Port A1 1 = input 0 = output 1 on power up |                                                                 |            |               |  |  |  |

| CWnD5 | 0 or 1 (no effect)                         |                                                                 |            |               |  |  |  |

| CWnD6 | 0 or 1 (no effect)                         |                                                                 |            |               |  |  |  |

| CWnD7 | 0 or 1 (no effect)                         |                                                                 |            |               |  |  |  |

|   | Control Word (X = 0) |   |   |   |   | Hex Value |     |     | Port Setup |         |

|---|----------------------|---|---|---|---|-----------|-----|-----|------------|---------|

| 5 | 4                    | 3 | 2 | 1 | 0 |           | Α   | В   | C Upper    | C Lower |

| Х | 0                    | 0 | Х | 0 | 0 | 80        | Out | Out | Out        | Out     |

| Х | 0                    | 0 | Х | 0 | 1 | 81        | Out | Out | Out        | In      |

| Х | 0                    | 0 | Х | 1 | 0 | 82        | Out | In  | Out        | Out     |

| Х | 0                    | 0 | Х | 1 | 1 | 83        | Out | In  | Out        | In      |

| Х | 0                    | 1 | Х | 0 | 0 | 88        | Out | Out | ln         | Out     |

| Х | 0                    | 1 | Х | 0 | 1 | 89        | Out | Out | ln         | In      |

| Х | 0                    | 1 | Х | 1 | 0 | 8A        | Out | In  | ln         | Out     |

| Х | 0                    | 1 | Х | 1 | 1 | 8B        | Out | In  | ln         | In      |

| Х | 1                    | 0 | Х | 0 | 0 | 90        | In  | Out | Out        | Out     |

| Х | 1                    | 0 | Х | 0 | 1 | 91        | ln  | Out | Out        | In      |

| Х | 1                    | 0 | Х | 1 | 0 | 92        | ln  | In  | Out        | Out     |

| Х | 1                    | 0 | X | 1 | 1 | 93        | ln  | In  | Out        | In      |

| Х | 1                    | 1 | Х | 0 | 0 | 98        | ln  | Out | ln         | Out     |

| Х | 1                    | 1 | Х | 0 | 1 | 99        | ln  | Out | ln         | In      |

| Х | 1                    | 1 | Х | 1 | 0 | 9A        | ln  | In  | ln         | Out     |

| Х | 1                    | 1 | Χ | 1 | 1 | 9B        | ln  | In  | ln         | ln      |

### **Interrupt Control**

When enabled interrupts are generated on port bit A0 of each port (pin 47 on each 50 pin header), the port A0 must be set as an input.

#### X = port number

| IRQENX | interrupt enable | 1 = enabled                     | 0 = disabled (0 on power up) |  |  |  |  |

|--------|------------------|---------------------------------|------------------------------|--|--|--|--|

| IRQCX0 |                  | Interrupt mode select see table |                              |  |  |  |  |

| IRQCX1 |                  | Interrupt mode select see table |                              |  |  |  |  |

## **Interrupt Mode Select Table**

| IRQCn1 | IRQCn0 | INT Type     |

|--------|--------|--------------|

| 0      | 0      | Low level    |

| 0      | 1      | High level   |

| 1      | 0      | Falling edge |

| 1      | 1      | Rising edge  |

### **Interrupt Read**

Reading the INTSTAT port (Base+5) clears any interrupt pending.

| IRQST1 | (D0) Interrupt status | 1 = interrupt pending, 0 = none |

|--------|-----------------------|---------------------------------|

| IRQST2 | (D4) Interrupt status | 1 = interrupt pending, 0 = none |

## **Electrical Characteristics**

The PIO-48.PC104 uses 74LS245 octal bi-directional transceivers to provide TTL input/output capabilities. Each bit is pulled to +5V through a 10K ohm pull-up resistor to ensure each bit is at a known state when not driven.

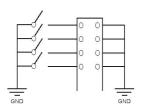

#### Input Circuit Schematic

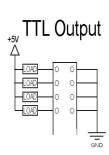

#### **Output Circuit Schematic**

## **Specifications**

## Inputs

| Logic High | Min 2VDC   |

|------------|------------|

| Logic Low  | Max 0.8VDC |

## **Outputs**

| Logic High | Min 2VDC @ 15mA    |

|------------|--------------------|

| Logic Low  | Max 0.55VDC @ 24mA |

## **Recommended Operating Conditions**

| Inputs | Min 0V    |

|--------|-----------|

| Inputs | Max 5.25V |

| Source | 15mA      |

| Sink   | 24mA      |

## **Temperature Range**

| Operating | 0°C - 70°C    |

|-----------|---------------|

| Storage   | -50°C - 105°C |

## **Power Consumption**

| Supply line | +5 VDC |

|-------------|--------|

| Rating      | 794 mA |

## **Physical Dimensions**

| Length | 3.550 inches (9.017cm) |

|--------|------------------------|

| Height | 3.775 inches (9.589cm) |

## **Example Circuits**

TTL Input

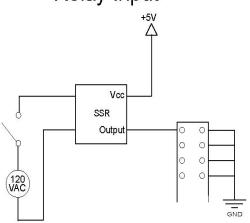

### Solid State Relay Input

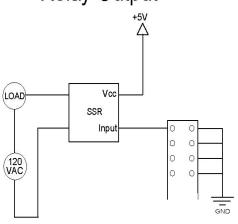

### Solid State Relay Output

## **Appendix A – Troubleshooting**

The adapter should provide years of trouble-free service. However, in the event that device appears to not be functioning incorrectly, the following tips can eliminate most common problems without the need to call Technical Support.

- 1. **Install software first**. After installing the software then proceed to adding the hardware. This places the required installation files in the correct locations.

- 2. Read this manual thoroughly before attempting to install the adapter in your system.

- 3. Use Device Manager under Windows to verify proper installation.

- 4. Use the SealO Control Panel applet or the Device Manager's property page for card identification and configuration.

- 5. Always use the Sealevel Systems diagnostic software when troubleshooting a problem. This will eliminate any software issues from the equation.

If these steps do not solve your problem, please call Sealevel Systems' Technical Support, (864) 843-4343. Our technical support is free and available from 8:00 A.M.-5:00 P.M. Eastern Time Monday through Friday. For email support contact <a href="mailto:support@sealevel.com">support@sealevel.com</a>.

## **Appendix B – How To Get Assistance**

Please refer to Troubleshooting Guide prior to calling Technical Support.

- 1. Begin by reading through the Trouble Shooting Guide in Appendix A. If assistance is still needed please see below.

- 2. When calling for technical assistance, please have your user manual and current adapter settings. If possible, please have the adapter installed in a computer ready to run diagnostics.

- 3. Sealevel Systems provides an FAQ section on its web site. Please refer to this to answer many common questions. This section can be found at <a href="http://www.sealevel.com/faq.htm">http://www.sealevel.com/faq.htm</a>.

- 4. Sealevel Systems maintains a Home page on the Internet. Our home page address is <a href="https://www.sealevel.com">www.sealevel.com</a>. The latest software updates, and newest manuals are available via our FTP site that can be accessed from our home page.

- 5. Technical support is available Monday to Friday from 8:00 a.m. to 5:00 p.m. Eastern time. Technical support can be reached at (864) 843-4343.

RETURN AUTHORIZATION MUST BE OBTAINED FROM SEALEVEL SYSTEMS BEFORE RETURNED MERCHANDISE WILL BE ACCEPTED. AUTHORIZATION CAN BE OBTAINED BY CALLING SEALEVEL SYSTEMS AND REQUESTING A RETURN MERCHANDISE AUTHORIZATION (RMA) NUMBER.

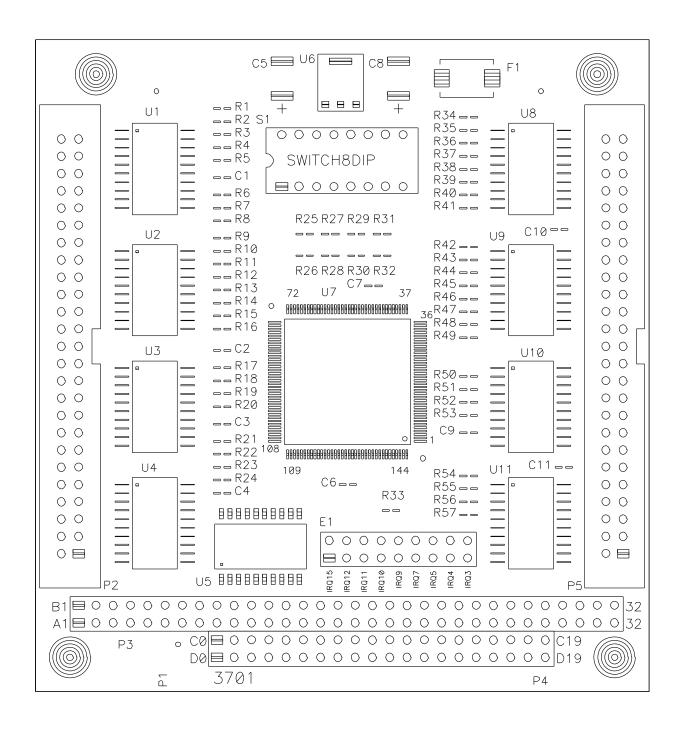

## Appendix C – Silk Screen – 3701 PCB

## **Appendix D – Compliance Notices**

### Federal Communications Commission (FCC) Statement

This equipment has been tested and found to comply with the limits for Class A digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference in such case the user will be required to correct the interference at the user's expense.

#### **FMC Directive Statement**

Products bearing the CE Label fulfill the requirements of the EMC directive (89/336/EEC) and of the low-voltage directive (73/23/EEC) issued by the European Commission. To obey these directives, the following European standards must be met:

- EN55022 Class A "Limits and methods of measurement of radio interference characteristics of information technology equipment"

- **EN55024** "Information technology equipment Immunity characteristics Limits and methods of measurement".

This is a Class A Product. In a domestic environment, this product may cause radio interference in which case the user may be required to take adequate measures to prevent or correct the interference.

Always use cabling provided with this product if possible. If no cable is provided or if an alternate cable is required, use high quality shielded cabling to maintain compliance with FCC/EMC directives

## Warranty

Sealevel's commitment to providing the best I/O solutions is reflected in the Lifetime Warranty that is standard on all Sealevel manufactured I/O products. We are able to offer this warranty due to our control of manufacturing quality and the historically high reliability of our products in the field. Sealevel products are designed and manufactured at its Liberty, South Carolina facility, allowing direct control over product development, production, burn-in and testing. Sealevel achieved ISO-9001:2015 certification in 2018.

### **Warranty Policy**

Sealevel Systems, Inc. (hereafter "Sealevel") warrants that the Product shall conform to and perform in accordance with published technical specifications and shall be free of defects in materials and workmanship for the warranty period. In the event of failure, Sealevel will repair or replace the product at Sealevel's sole discretion. Failures resulting from misapplication or misuse of the Product, failure to adhere to any specifications or instructions, or failure resulting from neglect, abuse, accidents, or acts of nature are not covered under this warranty.

Warranty service may be obtained by delivering the Product to Sealevel and providing proof of purchase. Customer agrees to ensure the Product or assume the risk of loss or damage in transit, to prepay shipping charges to Sealevel, and to use the original shipping container or equivalent. Warranty is valid only for original purchaser and is not transferable.

This warranty applies to Sealevel manufactured Product. Product purchased through Sealevel but manufactured by a third party will retain the original manufacturer's warranty.

### **Non-Warranty Repair/Retest**

Products returned due to damage or misuse and Products retested with no problem found are subject to repair/retest charges. A purchase order or credit card number and authorization must be provided in order to obtain an RMA (Return Merchandise Authorization) number prior to returning Product.

### How to obtain an RMA (Return Merchandise Authorization)

If you need to return a product for warranty or non-warranty repair, you must first obtain an RMA number. Please contact Sealevel Systems, Inc. Technical Support for assistance:

Available Monday – Friday, 8:00AM to 5:00PM EST

Phone 864-843-4343

Email <a href="mailto:support@sealevel.com">support@sealevel.com</a>

### **Trademarks**

Sealevel Systems, Incorporated acknowledges that all trademarks referenced in this manual are the service mark, trademark, or registered trademark of the respective company.